## University of South Florida **Scholar Commons**

**Graduate Theses and Dissertations**

Graduate School

November 2020

# Reading and Programming Spintronic Devices for Biomimetic **Applications and Fault-tolerant Memory Design**

Kawsher Ahmed Roxy University of South Florida

Follow this and additional works at: https://scholarcommons.usf.edu/etd

Part of the Electrical and Computer Engineering Commons

#### **Scholar Commons Citation**

Roxy, Kawsher Ahmed, "Reading and Programming Spintronic Devices for Biomimetic Applications and Fault-tolerant Memory Design" (2020). Graduate Theses and Dissertations. https://scholarcommons.usf.edu/etd/8584

This Dissertation is brought to you for free and open access by the Graduate School at Scholar Commons. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of Scholar Commons. For more information, please contact scholarcommons@usf.edu.

## Reading and Programming Spintronic Devices for Biomimetic Applications and Fault-tolerant Memory Design

by

Kawsher Ahmed Roxy

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy Department of Electrical Engineering College of Engineering University of South Florida

Major Professor: Sanjukta Bhanja, Ph.D.

Wilfrido A. Moreno, Ph.D.

Ismail Uysal, Ph.D.

Rasim Guldiken, Ph.D.

Ravi Panchumarthy, Ph.D.

Date of Approval: November 12, 2020

Keywords: Spintronics, Transverse Read, Domain Wall Memory, Non-Volatile Memory, In-Memory Computation

Copyright © 2020, Kawsher Ahmed Roxy

## Dedication

This dissertation is dedicated to

My Parents

My Wife, Arifa

My Daughter, Rayyan

My Brother

#### Acknowledgments

Finally, the journey is nearing its end. There are many who helped me along the way on this journey through their guidance, support and care. First, I would like to express my utmost gratitude to my graduate advisor, Dr. Sanjukta Bhanja, who was always happy to discuss research ideas and provide guidance, constant encouragement, and precious professional and personal advice. Specially at the struggling moments, her continuous support made graduate school an incredibly rewarding experience. I would like to thank my committee members, Dr. Wilfrido Moreno and Dr. Ismail Uysal, Dr. Rasim Guldiken, Dr. Ravi Panchumarthy and the chairperson of my defense, Dr. Kingsley Reeves. Without their guidance, I would not have made it.

I would like to thank several other faculty members from whom I have learned a lot and who have given me valuable academic and career advice. Those professors include Dr. Sylvia Thomas, Dr. Srinivash Kathkoori, and Dr. Jorge Galvis. I also want to thank the staff of the EE main office for their help and the entire department for their warmth and welcoming manner.

My acknowledgement would be incomplete without thanking my wonderful friends for their significant supports during my journey towards this degree. I especially want to thank Abir with whom I discussed research ideas for hours. Here comes to thank Imran, Inteha, Shiblee, Tirtha, Dewan for all the fun-filled tours and memorable moments. This is also the time to thank Hasnat, Shuvo, Adnan, Safi, Ridita, Zahangir, Arindam, Arif, Sampad, Jakir for their encouragement. I must also thank my great labmates: Ilia, Pavia, Prayash for their unconditional support.

Finally, to my wife, Arifa, and my daughter, Rayyan: your love and understanding helped me through the challenging times. For the last five years the person whose contributions are the most is my wonderful wife, Arifa. I am also blessed to have her as my colleague. Without you believing in me, I never would have made it. My achievements and this dissertation remain incomplete without acknowledging the unconditional love and support that I got from my parents and brother.

## **Table of Contents**

| List of Tabl | es                                                            | iv          |

|--------------|---------------------------------------------------------------|-------------|

| List of Figu | res                                                           | v           |

| Abstract     |                                                               | vii         |

| Chapter 1:   | Introduction                                                  | 1           |

| 1.1          | Conventional CMOS Memories                                    | 2           |

| 1.2          | Emerging Memories: Spintronic Memories                        | 4           |

| 1.3          | Spintronic Memories in Bio-Mimetic Computing Architectures    | 6           |

| 1.4          | Contribution                                                  | 7           |

| 1.5          | Outline of the Dissertation                                   | 9           |

| Chapter 2:   | Spintronic Memories                                           | 11          |

| 2.1          | Single Domain Nanomagnet                                      | 11          |

| 2.2          | Multilayer Spintronic Devices                                 | 12          |

| 2.3          | Magnetic Tunnel Junction                                      | 13          |

|              | 2.3.1 Tunnel Magnetoresistance                                | 14          |

|              | 2.3.2 Spin Transfer Torque (STT)                              | 16          |

|              | 2.3.3 CMOS Integration                                        | 19          |

| 2.4          | Spin Valve                                                    | 19          |

| 2.5          | Domain Wall Memories                                          | 20          |

| 2.6          | Application of Spintronic Devices                             | 21          |

|              | 2.6.1 Memory Applications                                     | 22          |

|              | 2.6.2 GMR Sensors                                             | 22          |

|              | 2.6.3 Spin Torque Nano-Oscillator                             | 23          |

|              | 2.6.4 All-Spin Logic Device (ASLD)                            | 24          |

|              | 2.6.5 Nanomagnetic Energy Minimizing Co-processor             | 25          |

| 2.7          | Conclusion                                                    | 26          |

| Chapter 3:   | Reading of Magnetic Energy Minimizing Co-Processor            | 27          |

| 3.1          | Introduction                                                  | 27          |

| 3.2          | Quadratic Optimization via Energy Minimization of Nanomagnets | 28          |

|              | 3.2.1 A Case Study-Perceptual Grouping in Computer Vision     | 28          |

|              | 3.2.2 Total Magnetic Energy in the Magnetic System            | 29          |

|              | 3.2.3 Mapping the Optimization Problem to the Magnetic System |             |

| 9.9          | 3.2.4 Translating Output of the Problem from Magnetic States  | 31          |

| 3.3          | Electrical Reading of the Output                              | 31          |

| 9.4          | 3.3.1 Structure and Resistance Modelling of a Cell            | 32          |

| 3.4          | Reading Schemes                                               | 33          |

|              |                                                               | i           |

| للاستشارات   |                                                               |             |

|              | · ·                                                           | www.manaraa |

|              |                                                               |             |

|            | 3.4.1 Reference Resistor Based Reading                               | 35       |

|------------|----------------------------------------------------------------------|----------|

|            | 3.4.2 Reference Cell Based Reading                                   | 36       |

|            | 3.4.3 Differential Reading                                           | 37       |

| 3.5        | Improving the Sense Margin                                           | 38       |

| 3.6        | Conclusion                                                           | 40       |

| Chapter 4: | Programmable Magnetic Grid                                           | 41       |

| 4.1        | Introduction                                                         | 41       |

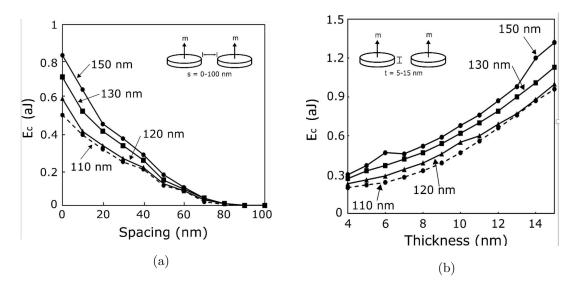

| 4.2        | Theoretical Analysis                                                 | 42       |

| 4.3        | Coupling Energy Estimation                                           | 42       |

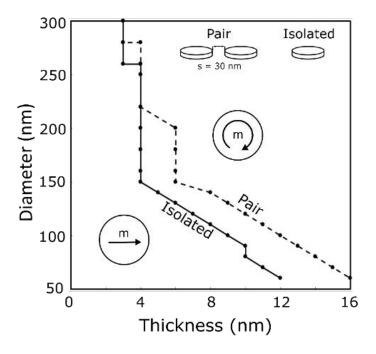

| 4.4        | CoFeB Phaseplot                                                      | 46       |

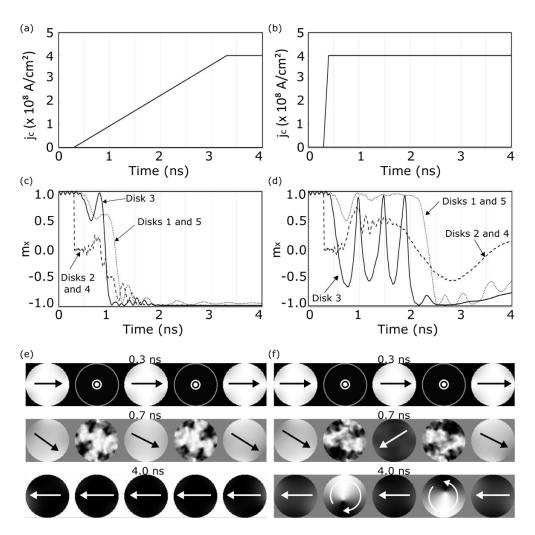

| 4.5        | SOT-based Reconfiguration in a Magnetic Array                        | 47       |

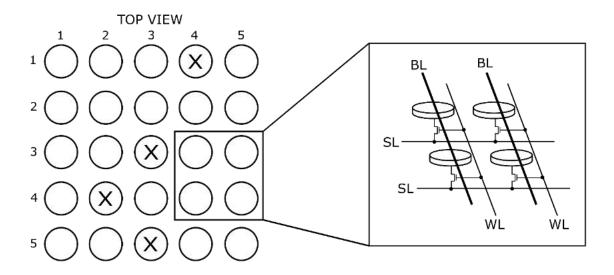

| 4.6        | A Programmable Magnetic Grid                                         | 49       |

| 4.7        | Conclusion                                                           | 50       |

| Chapter 5: | Transverse Read in Domain Wall Memories                              | 52       |

| 5.1        | Introduction                                                         | 52       |

| 5.2        | Domain Wall Memory Nanowire                                          | 53       |

|            | 5.2.1 DWM Read, Write and Shift Operation                            | 53       |

| 5.3        | Transverse Read                                                      | 55       |

|            | 5.3.1 Motivation                                                     | 55       |

| F 4        | 5.3.2 Theoretical Analysis                                           | 56       |

| 5.4        | Simulation Setup                                                     | 59       |

|            | 5.4.1 Transverse Read Current                                        | 61       |

| <b>.</b>   | 5.4.2 Device Operation During Transverse Read Results and Discussion | 62       |

| 5.5        | 5.5.1 Resistance Deviation Due to Process Variation                  | 63<br>64 |

| 5.6        | Parallel TRs for Longer Nanowires                                    | 65       |

| 5.0        | 5.6.1 Comparison Between Transverse Read and Conventional Read       | 67       |

| 5.7        | Transverse Error Correction Coding                                   | 67       |

| 5.8        | Conclusion                                                           | 69       |

| 0.0        | Conclusion                                                           | 0.0      |

| Chapter 6: | Pinning Fault in Domain Wall Memories                                | 70       |

| 6.1        | Introduction                                                         | 70       |

|            | 6.1.1 Faults During Shifting                                         | 71       |

| 6.2        | Domain Wall and Pinning Sites                                        | 72       |

| 0.0        | 6.2.1 Pinning of DW                                                  | 73       |

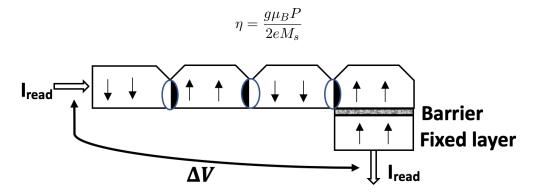

| 6.3        | Modeling a Deformed Notch                                            | 74       |

| C 4        | 6.3.1 Modeling the Deformed Side                                     | 75<br>76 |

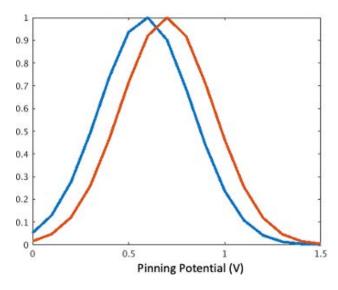

| 6.4        | Variation of Pinning Potential with Process Variation                | 76       |

| 6.5        | Results and Discussion                                               | 77       |

| 6.6        | Conclusion                                                           | 79       |

| Chapter 7: | Conclusion and Future Work                                           | 80       |

| 7.1        | Synopsis                                                             | 80       |

| 7.2        | Future Work                                                          | 81       |

|            |                                                                      |          |

| References                        | 82       |

|-----------------------------------|----------|

| Appendix A: Copyright Permissions | 95       |

| About the Author                  | End Page |

## List of Tables

| Table 1.1: | Comparison between traditional and emerging memories.                |    |

|------------|----------------------------------------------------------------------|----|

| Table 2.1: | Definition of parameters used in this chapter.                       | 17 |

| Table 3.1: | Current requirements for reading the cells.                          | 39 |

| Table 3.2: | Sense margin improvement by using pre-amplifier.                     | 40 |

| Table 3.3: | Comparison between different methods.                                | 40 |

| Table 5.1: | Material properties for NiFe and CoFeB-MgO used in simulation.       | 60 |

| Table 5.2: | Definition of symbols used in this chapter.                          | 6. |

| Table 5.3: | Comparative analysis of IMA and PMA nanowires.                       | 65 |

| Table 5.4: | Performance comparison between conventional and transverse read . $$ | 67 |

| Table 6.1: | Material properties used in 16-bit nanowire simulation.              | 77 |

## List of Figures

| Figure | 1.1:  | A typical memory hierarchy in a conventional von Neumann architecture. | 2  |

|--------|-------|------------------------------------------------------------------------|----|

| Figure | 1.2:  | Conventional CMOS memories.                                            | 3  |

| Figure | 1.3:  | Emerging devices and non-Boolean frameworks.                           | 7  |

| Figure | 2.1:  | Spin based devices.                                                    | 13 |

| Figure | 2.2:  | Different layers and ground states of an MTJ.                          | 13 |

| Figure | 2.3:  | Band diagram in two ground states.                                     | 15 |

| Figure | 2.4:  | Different torques involved in switching mechanism.                     | 17 |

| Figure | 2.5:  | The STT effect caused by the electron flow.                            | 18 |

| Figure | 2.6:  | An MTJ cell is integrated with an access transistor.                   | 19 |

| Figure | 2.7:  | Structure and access ports of an DWM nanowire.                         | 21 |

| Figure | 2.8:  | Basic configuration and output of an STNO.                             | 23 |

| Figure | 2.9:  | Anatomy of a basic all spin logic Device.                              | 24 |

| Figure | 2.10: | A sketch of the nanomagnetic co-processor.                             | 25 |

| Figure | 3.1:  | Steps involved in problem mapping into nanomagnetic co-processor.      | 30 |

| Figure | 3.2:  | Magnetic state variables.                                              | 31 |

| Figure | 3.3:  | Resistance calculation due to process variation.                       | 32 |

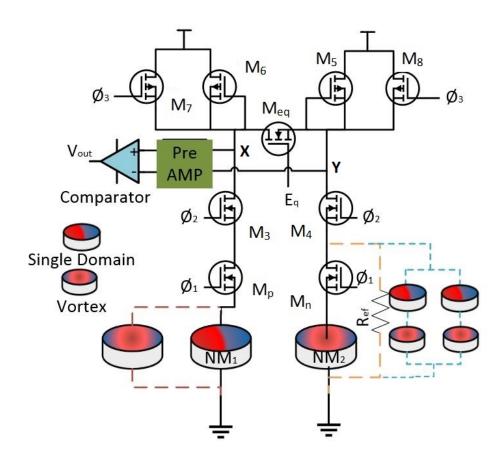

| Figure | 3.4:  | Read circuit to read magnetic states.                                  | 34 |

| Figure | 3.5:  | Variation tolerance of the circuit in reference resistance mechanism.  | 35 |

| Figure | 3.6:  | Variation tolerance of the circuit in differential read mechanism.     | 37 |

| Figure | 3.7:  | Pre-amplifier stage of the comparator.                                 | 38 |

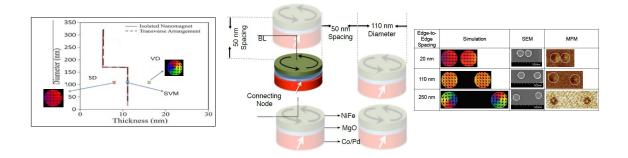

| Figure | 4.1:  | Extension and comparison of simulation results with MFM micrographs.   | 43 |

| Figure | 4.2:  | The disk dimensions and layouts associated with the simulations.       | 44 |

| Figure | 4.3:  | Magnetic coupling energy.                                              | 45 |

| Figure 4.4:  | Phase-plot of a CoFeB nanodot.                                              | 46 |

|--------------|-----------------------------------------------------------------------------|----|

| Figure 4.5:  | SOT-mediated programmable array of nanomagnets.                             | 47 |

| Figure 4.6:  | A hypothetical magnetic layout with SOT-based reconfigurability.            | 50 |

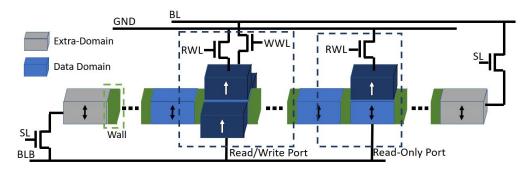

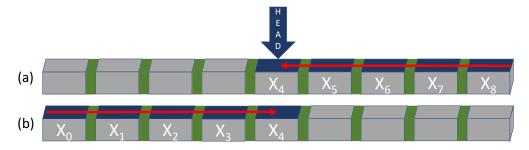

| Figure 5.1:  | Anatomy of a typical DWM nanowire.                                          | 53 |

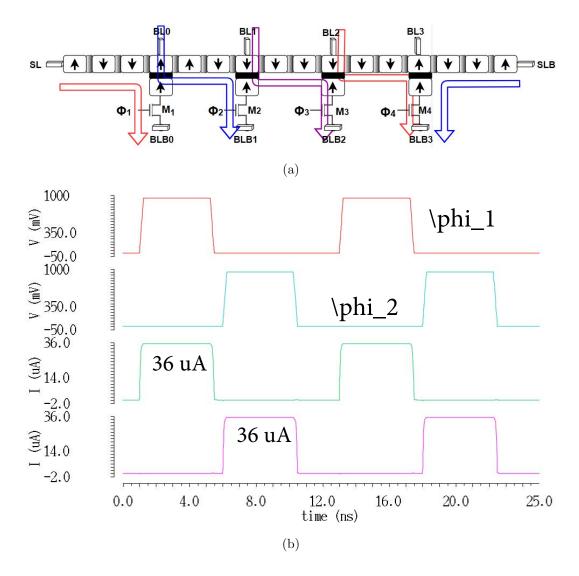

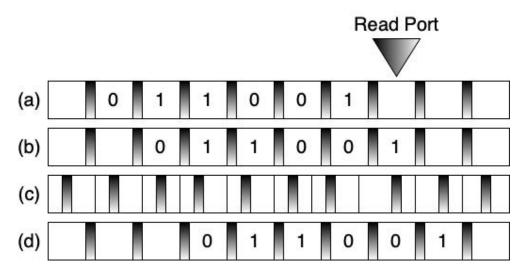

| Figure 5.2:  | Signals associated with read, write and shift operation.                    | 54 |

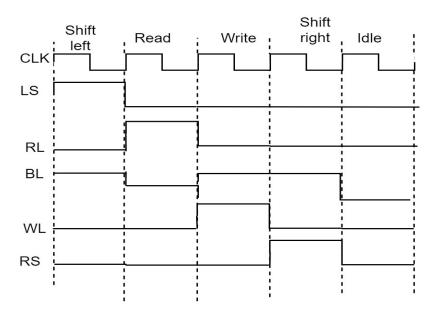

| Figure 5.3:  | Conduction electrons bend at the wall exerting a force on the wall.         | 57 |

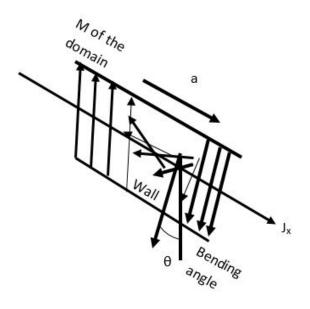

| Figure 5.4:  | The DWM segment used for simulation.                                        | 59 |

| Figure 5.5:  | A transverse read in both directions                                        | 62 |

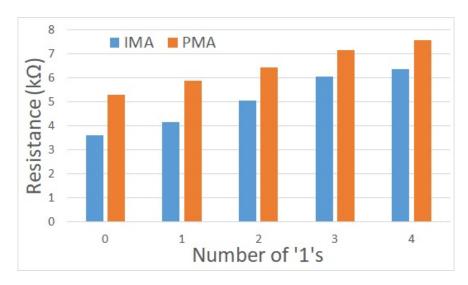

| Figure 5.6:  | Resistance values of IMA and PMA nanowires for different combinations.      | 63 |

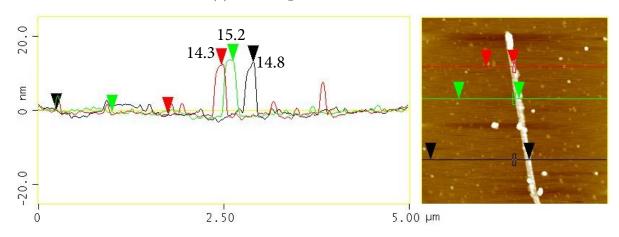

| Figure 5.7:  | Analysis of variation of CoFeB DW nanowire.                                 | 64 |

| Figure 5.8:  | Parallel TR study for longer nanowires                                      | 66 |

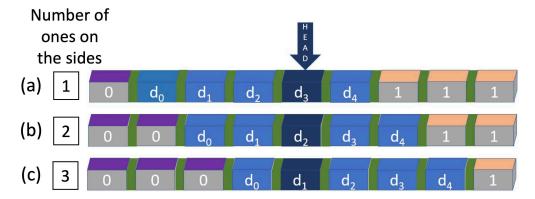

| Figure 5.9:  | Number of ones on the sides for different positions.                        | 68 |

| Figure 6.1:  | Position errors during shifting.                                            | 71 |

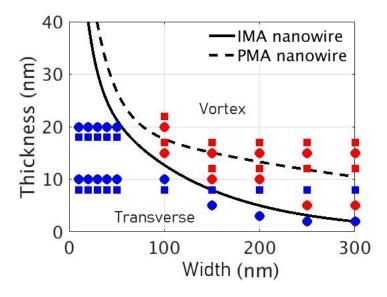

| Figure 6.2:  | Phase boundary between transverse and vortex wall.                          | 72 |

| Figure 6.3:  | A domain wall is pinned at a triangular notch.                              | 73 |

| Figure 6.4:  | A 4-domain nanowire with one deformed notch.                                | 74 |

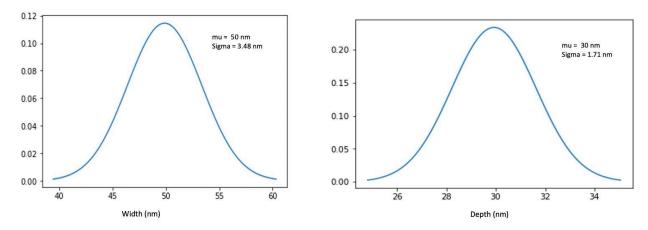

| Figure 6.5:  | Normal distribution of notch's width and depth.                             | 75 |

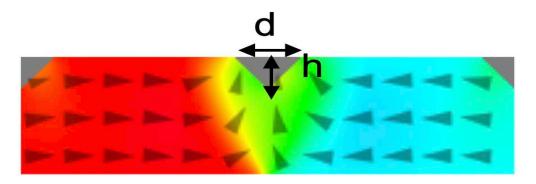

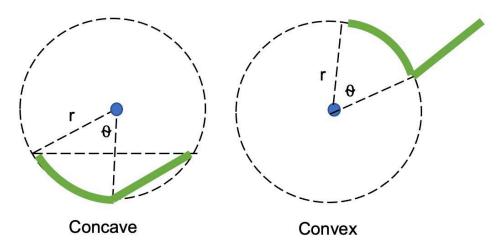

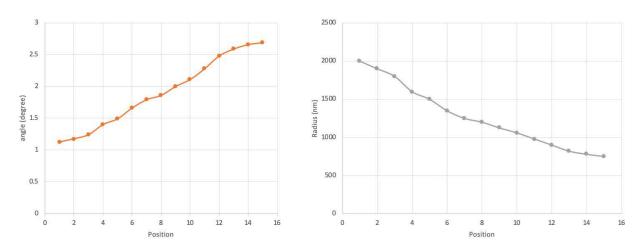

| Figure 6.6:  | Modeling the curvature of the deformity.                                    | 76 |

| Figure 6.7:  | Angle and radius of notch to achieve shift current for different positions. | 76 |

| Figure 6.8:  | Pinning potential variation with the deformities in a notch.                | 77 |

| Figure 6.9:  | A domain wall nanowire with 4 domains.                                      | 77 |

| Figure 6.10: | Domain wall displacement with applied current pulses for shifting.          | 78 |

| Figure 6.11: | Critical current variation with deformities.                                | 79 |

#### Abstract

Despite the triumph of conventional computing architectures till today, there emerges a lot of computing problems that are solved poorly by them. The reason behind this are twofold: i) the computing algorithm is incompetent in solving those problems, and ii) non-ideal effects of the traditional device technologies outperforms the benefits of using them. Hence, extensive research efforts have been put to devise novel algorithms as well as new devices. Among them spintronic devices demonstrate better performance in traditional architectures as well as offers way better solution to a lot of new problems when bundled with unconventional computing algorithms. Apart form being used as data-storage, spintronic devices are also leveraged as computing elements in many recently proposed architectures as the underlying device physics can directly solve many problems. However, the benefits of using them as computing elements become reduced or diminished because the peripherals of these architectures are based on conventional technologies. Specially the reading and programming mechanisms are not straightforward. In this dissertation, we have explored the challenges and developed the three reading techniques for a new computing framework based on spintronic devices. These nano-structured devices are prone to process variations which can significantly impair the read operation. We have addressed the process variations and modified the read techniques to combat the non-ideal effects. We have also devised a spin-orbital torquemediated programmable magnetic grid that can solve multiple instances of a problems in same hardware. One particular spintronic device is domain wall memories. Though these memories offer high density and low power operation, they suffer from inaccurate shifting due to various faults. In this dissertation, we have discussed a novel transverse read technique to generate error correction codes to mitigate different faults. Lastly, we have modeled a new type of shifting faults, known as pinning faults, in domain wall memories due to the process variations. We have developed a analytical model of geometric variation, and characterized the fault using the critical shift current.

#### Chapter 1: Introduction

Recent decades experience a hike in technological innovations; a simple example can be "the on-board computer in Apollo 11 has a random-access-memory (RAM) of 32kbits and read-only-memory (ROM) of 72kbits" [1], whereas a typical smartphone contains 4Gbytes of RAM and up to 512Gbytes of storage, and easily fits in a pocket. This infers the pervasive nature of modern technologies and demonstrates how these technologies widen the capability of a human. Day-by-day with the evolution of internet-of-things, every instances of life are going to be interconnected and can be controlled by a hand-held device using a thumb. However, these benefits come with increasing challenges of obtaining ultra-fast information processing, low power consumption, expanded data storage, data security with additional expectation of miniature devices. The question arises here: 'Are the traditional architectures capable to handle the increased computational demands?'.

This question is very fundamental, and answer to this question depends on the performance of individual components of conventional architecture. In a broad view, modern electronics are built on von Neumann architecture, where a central processing unit (CPU) computes the data stored in memories at different levels. This requires back-and-forth fetching of data from memory hierarchy and CPU. The key bottleneck of this architecture is the mismatch between the processing speed and data-fetching speed. In addition to that, two most accessed semiconductor memories by CPU, cache and random access memories (RAMs), are of low capacity due to bulkiness and consumes a great deal of energy due to non-volatility. Despite the fact that high-scalability increases the density of these memories to free more real estate to accommodate additional resources for computation, ultra-miniaturization increases the non-ideal effects significantly, and combating these effects nullify the benefits.

Another major drawback of traditional Boolean architecture is synthesizing all problems into similar framework. Parallel processing in modern computers increase the computing speed highly, there exists a lot of problems that cannot be effectively parallelized without compromising the accu-

racy. These problems often can be solved with much efficiency by different algorithms. Therefore, there is a hike in research on unconventional computing algorithms e.g. non-Boolean computation, neuromorphic computing, neural networks, in-memory computation, hierarchical temporal memory, Ising model etc. in recent years to target those problems. Many of these problems are heavily data-centric and require data storage with much higher capacity, and faster accessible with less amount of power consumption.

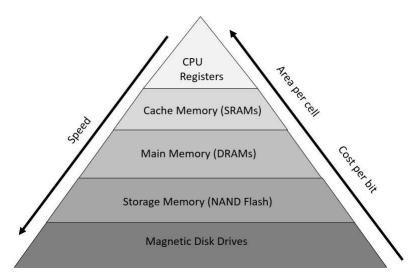

The evolution of these algorithms raise another question: 'Can the existing memory technologies cope with the novel algorithmic needs?'. Clearly, the conventional complimentary metal-oxide-semiconductor (CMOS) memories experience increased challenges to be compatible with innovative applications that are data-heavy, and often require centi-second processing speed. The CMOS memories achieve immense success, even till today, because there are different types of memories to be offered for target applications. To be more specific, Fig. 1.1 captures the typical memory hierarchy of a von Neumann architecture, where two basic types of memory: i) memory-class storage, ii) storage-class memory form a memory-management to process and store data.

Figure 1.1: A typical memory hierarchy in a conventional von Neumann architecture.

#### 1.1 Conventional CMOS Memories

Two memories in the top shelf of the hierarchy i.e. central processing unit (CPU) registers, static random access memories (SRAMs) [2] are developed to contain and process instruction sets for computation. These memories are very fast in operation, but largest in size, and consume

a huge amount of power due to higher leakage currents. The main memory typically consists of dynamic random access memories (DRAMs) [3] which have much higher densities than CPU registers and SRAMs, but process data in a slower speed. The key issue with DRAMs is the non-volatile characteristic which requires a 'refresh' of the stored data in a regular interval. This additional requirement increases the power consumption overhead.

The main storage of this architecture is the highly dense storage-type memories e.g. NAND FLASH [4], Solid State Drives (SSD) [5], 3D XPoint [6], etc. The main feature of this class of memory is the non-volatility which means they can retain the stored data for a longer period of time without power. Despite having the advantage of non-volatility and the higher density, the write and read-speed is several orders of magnitude slower than the cache or main memory. Moreover, the power requirements for writing new data and accessing stored data are significantly high.

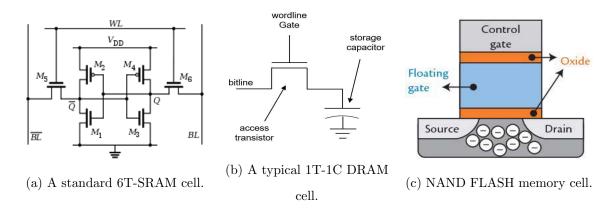

Figure 1.2: Conventional CMOS memories.

Fig. 1.2 portrays state-of-art CMOS memories in their basic configurations. A typical SRAM cell, shown in Fig. 1.2a, contains two cross-coupled inverters (four transistors) to store data and two access transistors to write and access the stored data. The density of SRAM memories is poor because of the 6 transistor requirement. The sub-threshold current flow through the access transistors during power-off causes charge-leakage of stored data, therefore requires a 'refresh' after a certain period to restore the data. Fig. 1.2b shows a standard DRAM cell of 1T-1C cell where, the capacitor stores the data as charge, and the access transistor is to write and access the data. The charge-decay from the capacitor requires re-writing the stored data periodically. DRAMs have much better density compared to SRAM, thus are utilized as main memory of a computing

architecture. Unlike SRAM and DRAM, the NAND FLASH memories, shown in Fig. 1.2c, is non-volatile, thus the periodic 'refresh' is unnecessary. Since a NAND FLASH memory cell is a transistor with an additional floating gate, this memory has the highest density which makes it perfect for data-storage. The writing process involves electron tunneling though a thin oxide layer from the floating gate and the bulk. The writing and reading speed of a FLASH memory are much slower than SRAM and DRAM counterpart.

From the above discussion it is evident that SRAM and DRAM can not be efficiently used as main storage due to non-volatility and lower density. On the contrary, FLASH memories or SSDs can not be used as main memory due to ultra-slow speed. Therefore, there always have been a quest to develop a utopian memory which is non-volatile, highly dense, faster like SRAM or beyond and consume less power.

#### 1.2 Emerging Memories: Spintronic Memories

In the decade of 2000, active research paradigm was to search for suitable alternative technologies that utilized charge transfer as the primary mode of computing. A few examples are Carbon Nanotube [7, 8], Graphene FET [9, 10], Tunnel FET [11, 12], Resonant tunneling diodes [13], Spin FET [14], Piezo [15] and NEMS [16]. However, there are other non-charge-based state variables like magnetization [17].

Table 1.1: Comparison between traditional and emerging memories based on key attributes [18, 19].

| Attributes                  | Traditional Memories |           |          | Emerging Memories |          |           |           |

|-----------------------------|----------------------|-----------|----------|-------------------|----------|-----------|-----------|

|                             | SRAM                 | DRAM      | FLASH    | FeRAM             | ReRAM    | PCRAM     | STT-MRAM  |

| Non-Volatility              | No                   | No        | Yes      | Yes               | Yes      | Yes       | Yes       |

| Cell Size (F <sup>2</sup> ) | 50-120               | 6-10      | 2        | 15-34             | 6-10     | 4-19      | 6-20      |

| Read time (ns)              | $\leq 2$             | 30        | $10^{3}$ | 5                 | 1-20     | 2         | 1-20      |

| Write time (ns)             | $\leq 2$             | 50        | $10^{6}$ | 10                | 50       | $10^{2}$  | 10        |

| Write power                 | Low                  | Low       | High     | Low               | Medium   | Low       | Low       |

| Endurance (cycles)          | $10^{16}$            | $10^{16}$ | $10^{5}$ | $10^{12}$         | $10^{6}$ | $10^{10}$ | $10^{15}$ |

| Scalability                 | Good                 | Limited   | Limited  | Limited           | Medium   | Limited   | Good      |

Memory technologies have seen an unprecedented growth. While 3D FLASH is the benchmark for non-volatile memories, many potential breakthroughs have happened through phase change memory (PCM) [20], ferroelectric RAM (FeRAM) [21], Spin-transfer-torque(STT)-MRAM [22, 23, 24]) and spintronic memories (Magnetoresistive Random Access Memory (MRAM) [25]. Table 1.1 compares the benchmark attributes of conventional memories with the emerging memories. Evidently, STT-MRAM possesses the desired features from the traditional memories as well as offers solutions to the bottlenecks of them. Hence, STT-MRAM can be the utopian memory which can make the idea of 'single-memory computing architecture' feasible. Since spintronic devices are the basis of STT-MRAM, most parts of this manuscript focus on magnetization as the state variable.

Another promising spintronic memory is domain wall memory (DWM) which, unlike other emerging memories, can store multiple bit in a single cell. Domain wall memories consist of long nanowires with multiple magnetic domains at regular interval. Each domain stores a single bit of data, and typically a nanowire can store 64-512 bits of data. The interesting characteristic of this type of memory is the adjacent placement of bits. This enables an additional important operation besides read and write with no extra technical overhead: shifting. The stored data in a DWM nanowire can be shifted in both direction making it a perfect candidate for cache memory. Additionally, higher density ensures maximum capacity of data-storage with domain wall memories.

Unlike the conventional electronics, the core principle of spintronic devices leverages both spin and charge properties of electrons, rather than exploiting only the charge property. Spin property of electrons faced significant ignorance in conventional logic and information processing. Earlier, spin was only exploited for magnetic recording in a macroscopic way [26], where the magnetization of ferromagnet is used. The microscopic manipulation of the spin for controlling electron transport in a device became possible after the discovery of "Giant Magnetoresistance (GMR)" [27, 28] in 1988. Subsequently, the development of spintronic devices triggered research in a broad range of application domains, such as highly sensitive magnetic-field sensors [29], magnetic read heads [30], and nonvolatile magnetic memory applications [31]. High density, radiation hardness, and long data retention make MRAM an excellent choice for data storage and main memory in applications under unfavorable conditions.

### 1.3 Spintronic Memories in Bio-Mimetic Computing Architectures

In a parallel endeavor, researchers have been mesmerized by the computation that occurs in nature and human brain. The energy efficiency clearly has significant supremacy over conventional Boolean processing for a multitude of complex tasks. While we do not have a clear understanding how the brain actually works, many hypotheses have emerged for bio-mimetic computing.

The spintronics research has already established various flavors of alternate non-von Neumann problem mapping like neuromorphic [32, 33, 34], and non-Boolean computing with oscillators [35, 36]. In general, coupled oscillators have shown to solve associative processes [37, 37, 38, 39]. Recently, pairwise coupling was experimentally demonstrated in [40]. Application-specific algorithms have been proposed for signal processing [41, 42, 43, 44] for a while.

| Devices                  |            | Non-Boolean Framework            |                       |                           |  |  |

|--------------------------|------------|----------------------------------|-----------------------|---------------------------|--|--|

|                          |            | Energy Minimization<br>Framework | Coupled<br>Oscillator | Neuromorphic<br>Framework |  |  |

| nics                     | Spin Valve |                                  | ~                     | ~                         |  |  |

| Spintronics              | MTJ        | V                                |                       |                           |  |  |

| Spi                      | STNO       |                                  | <b>V</b>              | V                         |  |  |

| Resistive/<br>Memristors |            |                                  |                       | <i>\</i>                  |  |  |

| Quantum Computing        |            | V                                |                       |                           |  |  |

| Conventional CMOS        |            | Graph Cut/Simulated<br>Annealing | <b>V</b>              | <i>V</i>                  |  |  |

Figure 1.3: Emerging devices and non-Boolean frameworks.

In energy minimization framework, briefly discussed in chapter 2 and 3, the computational theme is mapping the quadratic energy minimization problem spaces into a set of interacting magnets. This way the energy relationship between the problem variables is proportional to that of the dipolar coupling energies between the corresponding magnets. The optimization is actually accomplished by the relaxation physics of the magnets themselves, and solutions can be read-out in parallel. In essence, given a specific instance of the problem, a specific magnetic layout can be achieved, and the relaxed state of which will be the solution to the original problem. The key idea is that the nanomagnetic disks in a critical dimension settle into two different magnetization ground states: a vortex state when weakly coupled, or a single domain state when strongly coupled.

#### 1.4 Contribution

Although a good number of computing architectures harness the innate physical properties of spintronic devices for storage and computation, the peripherals of the hardware e.g. control circuits, sensing mechanisms, writing techniques are designed with conventional CMOS technologies. Spintronic devices are still in development phase to offer a homogeneous all-spintronic platforms.

Therefore, the integration with CMOS is imperative, and quite challenging. The hybridization process between these two technologies poses bilateral constraints on each other while integration.

In addition to these, the state variables in spintronic systems depend on the electrical excitations i.e. current, voltage. This implies there is a possibility the current for reading the data can switch the magnetization of the device, in other words, can alter the stored data. Apart from this in nanomagnetic energy minimization hardware, nanomagnets have to placed within a certain distance, typically 30 nm, which put a upper limit of CMOS technology to be integrated with CMOS technologies. Prior efforts [45, 46, 47] analyzed the constraints and mitigated the challenges of integration.

The primary version of magnetic energy minimizing co-processor (MEMCoP) lacks the electrical reading method. In this dissertation, we have discussed how the ground states in a spintronic computing hardware can be detected without altering the original output. We have devised three reading mechanisms, analyzed the trade-offs and compared their performances. We have also detailed the pre-amplifier used to increase the sense margin between the ground states. Typically, the circular nanomagnets used in MEMCoP have diameter ranging between 110-150 nm with thickness varying from 4-8 nm. The fabrication imperfection impairs the magnetic states of these nanoscale dots. Therefore, in this dissertation we have extended our read techniques to handle process variations.

Also, the initial-proof-of concept was demonstrated by fabricating a specific layout of nanomagnets for a specific problem. However, a more realistic architecture should be able to synthesize multiple instances of a problem in the same hardware. Parallel execution of multiple problems is desired too. That is why a developing programmable architecture is mandatory. Since the computing algorithm harnesses the diploar coupling between the nanomagnets, programmability can be achieved by counterbalancing the dipolar coupling. We have developed spin-orbital torque (SOT)-mediated programmable grid to reuse the hardware for a different set of problems. We have studied the current requirement for programming, and discovered that the ramp-up speed of applying current to generate SOT has significant impact on relaxation process.

Domain wall memories provide high density storage solution by storing more than one bits in a nanowire. Multiple bits share the same read port. During the reading process, the desired bit is shifted to the read port, and after reading, shifted back to its original position. Hence,

the traditional reading process involves two shifting making the read power higher. In many applications, it is necessary to determine the parity of data or the number of '1's (alternatively '0's) in the data. In such scenarios, conventional reading process is proven inefficient, power hungry, and slow. In this dissertation, we have discussed how a novel transverse read in a DWM nanowire can provide the global information of the stored data without shifting back and forth. This reduces significant power consumption and make the read process faster.

Bi-directional shifting of the stored data in a domain wall nanowire aids in logical and arithmetic operations i.e. multiplication, convolution etc. Generally, two different bits of data stored in two domains are separated by a varying magnetic boundary, known as domain wall. Domain walls are pinned to particular locations along the nanowires by intentionally patterning pinning sites. During the shift process, a domain wall is depinned from the site and travel to the next site and stays pinned there. However, process variations in pinning sites create non-uniform pinning strength at different positions. In that case, a wall with a higher pinning strength is not be depinned from the site for the critical shift current. This phenomenon is characterized by 'pinning fault'. Finally in this dissertation, we have analyzed how deformities in a notch can instigate pinning fault. We have also discussed a model to generate a distribution for variations of a notch. We envision that these contributions towards the use of spintronic devices in computing framework will resolve the key issues and benefit the overall nano-computing paradigm.

### 1.5 Outline of the Dissertation

- 1. Chapter 2 describes the fundamentals of key spintronic devices. The physics behind different operations are briefly discussed.

- 2. Chapter 3 discusses the read mechanisms developed to detect the ground states of magnetic energy minimizing co-processor. A brief discussion on the co-processor structure, and theory of operation is also included in this chapter.

- 3. Chapter 4 covers the SOT-medicated programmable nanomagnetic co-processor. This chapter also includes the analytical model of calculating pairwise dipolar coupling energy between two adjacent nanomagnets.

- 4. Chapter 5 details the transverse read technique in domain wall memories. A theoretical analysis along with the circuit level understanding have been discussed.

- 5. Chapter 6 contains the discussion on modeling the pinning fault occurred in domain wall memories.

- 6. Chapter 7 concludes the dissertation and sheds light on the future research direction.

#### Chapter 2: Spintronic Memories

Until the last decade of the twentieth century, the state-of-the-art mainstream electronics ignored spin, a critical degree of freedom of electrons. The superiority of the charge based technologies was beyond question until some drawbacks became apparent. These shortcomings triggered the research of different spin based emerging devices. Spintronic devices conform the group which exploits the spin of electrons for data storage or information processing. These devices utilize the interaction of spin of the carrier and the magnetic properties of the material. Combining the spin degree of freedom with the conventional charge-based devices, or the standalone spin-based devices enhance the performance of electronic systems. For data storage and information processing, magnets with ultra small dimensions are of crucial importance. The maturity of fabrication technologies to manufacture nanoscale devices has intrigued the research of magnets with deep sub-micron dimensions. Hence, a good number of spintronic devices have been proposed in recent few years. Some of them exhibit excellent performance and capability in memory and computing domain. In this chapter<sup>2.1</sup>, we will briefly cover some promising spintronic devices, as well as their theory of operation.

#### 2.1 Single Domain Nanomagnet

The fundamental cell of the spintronic devices is a mono-layer magnet [48] which contains its three dimensions within nanometer scale. The *Theory of Micromagnetics*, developed by Brown [49], models a nanomagnet as a single layer spin device. His theory explains how the interplay between quantum mechanical exchange and magnetostatic energies restrains the development of multiple magnetic domains in nanoscale particles. This behavior made possible the use of nanomagnets as switching devices, data storage, and computing elements.

<sup>&</sup>lt;sup>2.1</sup>Parts of this chapter was published in "Roxy, K. A., Bhanja, S. (2018). Non-Boolean Computing with Spintronic Devices. Foundations and Trends in Electronic Design Automation, 12(1), 1-123". Permission attached in Appendix <sup>Δ</sup>

Cowburn et al. [48] demonstrated the magnetic behavior of single domain circular nanomagnets. An annular nanomagnet can stay at any of its two ground states: single or vortex domain based on its diameter and thickness. An external magnetic field or a certain amount of current can switch the magnetization of the nanomagnet. Kumari et al. [50] studied the behavior of nanomagnets in a 2-D array based on their dimensions and spacing between the cells. Zhang et al. [51] demonstrated the generation of an intrinsic spin transfer torque from spin-orbit coupling without using another ferromagnetic layer.

Often in memory applications and computing paradigm, a grid of single domain nanomagnets is used purposely. Hence, the neighbor interaction between the nanomagnets in such a system is a critical factor. In memory applications, neighbor coupling hinders the functionality of a data storage; therefore it is not desired. As a result, the minimum space between nanomagnetic cells limits the density of the memory. However, in computing frameworks, the coupling between these nanomagnets is exploited in the implementation of some algorithms. In section 2.6.5, we will present an architecture based on single layer circular nanomagnets solving a quadratic optimization problem.

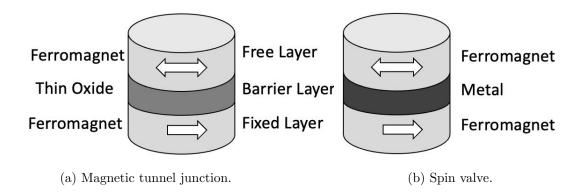

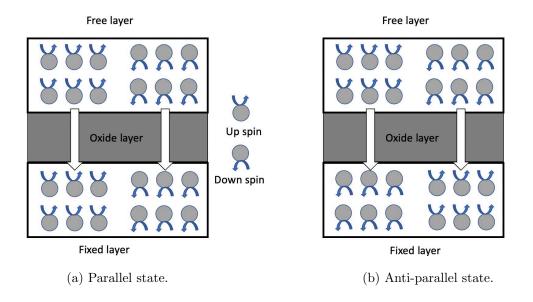

#### 2.2 Multilayer Spintronic Devices

Later, multi-layer stacked devices were introduced for more control and adaptability while solving different problems. In this scenario, a non-magnetic (NM) layer separates two single ferromagnetic (FM) layers. The type of the non-magnetic material divides the multi-layer devices into two groups: 1) GMR based devices such as a spin valve (SV) [52] in which the spacer layer is conductive, 2) TMR based devices such as Magnetic Tunnel Junction (MTJ) [53] which uses insulating oxide material as the spacer layer. One of the two ferromagnets acts as the fixed layer, and its magnetization is pinned to a particular direction. The other FM layer is the free layer, and its magnetization is manipulated to represent logic or solution to various problems. These multi-layer devices are magnetoresistive since their resistances rely on the relative magnetization of the fixed and free layer.

Figure 2.1: Spin based devices.

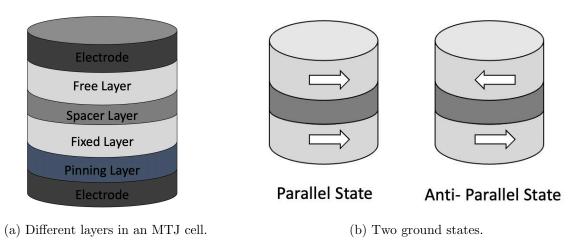

## 2.3 Magnetic Tunnel Junction

The core operational unit of a magnetic tunnel junction (MTJ) is a three-layer stack of materials in which the top and the bottom layers are ferromagnetic (FM), and the intermediate layer is an insulator (shown in Fig. 2.1b). The most prevailing structure (shown in Fig. 2.2a) of an MTJ is CoFeB (FM)/MgO (NM)/CoFeB (FM). The magnetization of the free layer (layer 1) can be manipulated to store data or process information while the magnetization of the fixed layer (layer 2) is kept firm. The fixed layer magnetization is pinned through an antiferromagnetic coupling with another ferromagnetic layer (layer 4) under it. A thin layer (layer 3) of Ruthenium (RU) is sandwiched between them to provide the maximum coupling.

Figure 2.2: (a) Different layers in an MTJ cell; (b) Two different ground states.

If the free layer magnetization is parallel to that of fixed layer, known as the parallel state, the resistance of the whole device is lower than when the device is in the anti-parallel state. The resistance differential can be termed as "Tunneling Magnetoresistance (TMR)" [54].

The resistance of an MTJ is dependent on the relative angle,  $\theta$ , between the magnetization of the free layer and the fixed layer. The conductance of an MTJ can be measured from the following equation:

$$G(\theta) = \frac{1}{2}(G_P + G_{AP}) + \frac{1}{2}(G_P + G_{AP})\cos(\theta)$$

(2.1)

where  $G_{AP}$  and  $G_P$  represent the conductance  $(G_P > G_{AP})$  of an MTJ in antiparallel  $(\theta = 180^0)$  state and parallel  $(\theta = 0^0)$  state respectively. The difference between these resistances is scaled down to define Tunnel Magnetoresistance (TMR) as in Eq. 2.2

$$TMR = \frac{G_P - G_{AP}}{G_{AP}} = \frac{R_{AP} - R_P}{R_P}$$

(2.2)

### 2.3.1 Tunnel Magnetoresistance

To understand the tunneling magnetoresistance (TMR) effect, at first, one has to analyze the band model that causes the variation in resistance. This difference arises when there is a change in the density of states of spin up and spin down electrons at Fermi level. In a case of a conventional tunneling process, the spin of electrons is conserved, since no spin-flip scattering mechanism is involved. This phenomenon directs the electrons of a specific spin from one electrode to tunnel into the states of another electrode. These states are unique to the spin orientation. In parallel magnetization orientation, the tunneling exchange occurs between the same band electrons. On the other hand, in antiparallel orientation, the tunneling exchange is forced to happen between the opposite band electrons. These events lead to a reduced number of states available for tunneling between the electrodes in the antiparallel configuration. They result in a higher tunneling resistance than parallel configuration.

Figure 2.3: Band diagram in (a) parallel, or (b) anti-parallel configuration.

The imbalance between majority and minority density of states at Fermi level causes the difference in TMR ratio [55]. The imbalance can be understood by the spin polarization factor,

$$P = \frac{(N \uparrow - N \downarrow)}{N \uparrow + N \downarrow} \tag{2.3}$$

where  $N\uparrow$  and  $N\downarrow$  are the number of spin-up and spin-down states available to contribute to the tunneling current.

The definition of TMR ratio with polarization factor can be written as:

$$TMR = \frac{2P_1P_2}{1 - P_1P_2} \tag{2.4}$$

where  $P_1$  and  $P_2$  are the polarization factors of the free layer and fixed layer.

TMR in real structure also depends on the properties of barrier material and other factors like electrode thickness, junction and electrode interface quality, bias voltage, etc. Depending on the crystal orientation (amorphous or crystalline) of the barrier layer, the device will behave differently. Two most favored tunnel barrier materials are AlOx and MgO.

#### 2.3.2 Spin Transfer Torque (STT)

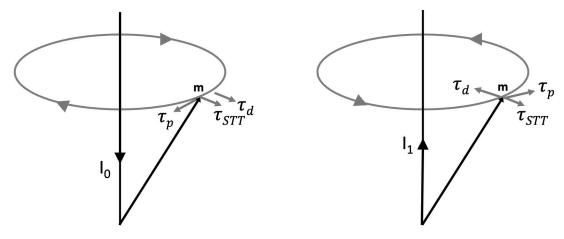

As the transportation of electrons in transition metal ferromagnets is spin-polarized, spin-transfer torque (STT) originates from this transfer process [56]. When a current flows through a magnetic nanostructure, there is an exchange interaction between the spin of conduction band electrons and the local moments. STT emerges when there is a non-collinearity between the spin current polarization and the local magnetization [56]. This torque can instigate several physical processes in the absence of applied magnetic field. Some of these are: domain wall movement along magnetic wires [57], magnetization reversal in nanopillars [58], and vortex displacement in magnetic dots [59].

Based on the direction of the current flow and the micromagnetic state, the spin-transfer torque can either expedite (leading to a stronger damping in the free layer) or offset (reducing the damping in the free layer) the relaxation processes. The magnetization of the free layer can be changed by either (1) external magnetic field, or (2) spin torque (generated by current passing through it). The free layer magnetization can be regulated by the following Landau-Lifshitz-Gilbert (LLG) equation with the STT term (Eq. 4.2) [60]:

$$\frac{d\vec{M_1}}{dt} = -\gamma M_s \vec{M_1} \times (\vec{H_{eff}} - \frac{\alpha}{\gamma M_s} \frac{d\vec{M_1}}{dt} + \frac{J_e g \hbar}{\mu_0 M_s^2 e t_F} \vec{M_1} \times \vec{M_2})$$

$$(2.5)$$

where,

$$\vec{H_{eff}} = \vec{H_{ext}} + \vec{H_k} + \vec{H_{demag}} + \vec{H_{ex}}$$

(2.6)

and

$$g = [-4 + (1+P)^3 \frac{(3+\hat{s_1}.\hat{s_2})}{4P^{3/2}}.$$

The parameters in the above equations are defined in Table 2.1. The first term on the right side of the Eq. 2.5 formulates how the resultant magnetic field (in Eq. 2.6) affects the free layer precessional dynamics. The second one addresses the damping in the free layer. The last part accounts for the impact of spin transfer torque (STT) on the free layer magnetization.

- (a) Write '0': STT expedites the relaxation.

- (b) Write '1': STT opposes the relaxation.

Figure 2.4: Different torques in the free layer of an MTJ cell during switching; (a) STT expedites the relaxation process, (b) STT opposes the relaxation process.

Table 2.1: Definition of parameters [46].

| Symbol                | Descriptions                                               |

|-----------------------|------------------------------------------------------------|

| $M_1$ , $M_2$         | Unit vectors of fixed and free layer magnetization.        |

| $M_s$                 | Saturation magnetization.                                  |

| $\gamma$              | Gyromagnetic ratio.                                        |

| $\vec{H_{eff}}$       | Unit vector in the direction of effective magnetic field.  |

| $\alpha$              | Gilbert damping constant.                                  |

| P                     | Spin polarizing factor.                                    |

| $n_{+/-}$             | Majority/Minority-state Fermi level spin densities [56].   |

| $\hat{s_1},\hat{s_2}$ | Unit vectors along the global spin orientation of the free |

|                       | and fixed layers.                                          |

| $t_F$                 | Thickness of free layer.                                   |

| e                     | Electron charge.                                           |

| $\hbar$               | Weighted Planck's constant.                                |

| $\mu_0$               | Permeability of free space.                                |

When the spin torque is significant enough, it can influence the free layer magnetization. When a current flows from free to fixed layer, the damping effect and the STT torque join to switch the magnetization of the free layer to parallel state [46]. The reverse current makes damping and STT work against each other. If the torque is more influential than the damping, the free layer will be switched to the antiparallel state ( shown in Fig. 2.4).

In this process, the torque generated by the tunneling current is used to change the magnetization. The spin transfer model states that the electrode with larger thickness polarizes the electrons of incoming current. As a result, the spin moment increases if the current density and the degree of polarization increase, producing torque. This spin torque can change the magnetization of the free layer in parallel or antiparallel direction on the reference layer (shown in Fig. 2.5). The direction of the STT reverses with reversing the current direction [55]. The critical current for switching the magnetization can be analytically expressed as [46]

$$J_{sw} = \frac{2e\alpha M_s t_F (H_k \pm H_{ext}) + 2\pi M_s}{\hbar \eta}$$

(2.7)

STT switching is promising, but the current requirement is still high. Therefore, some other techniques are still being researched to assist the STT switching mechanism, for example, thermally assisted switching [61], strain-assisted switching [62], etc.

Figure 2.5: The STT effect caused by the electron ow. The direction of the STT reverses with reversing the current direction [46].

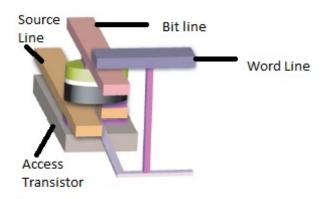

#### 2.3.3 CMOS Integration

To write and read an MTJ cell electrically, and achieve the selectivity for low power operation, nowadays MTJs are integrated with the state of the art CMOS technology. The most well known STT-MRAM architecture is a 2-D crossbar array of 1T-1C. Fig. 2.6 shows a primary MTJ cell with an access transistor as well as different control signal lines (SL, BL, WL). Applying suitable biases in these signals, an MTJ cell is written and read. As MTJ cells are thermally robust, they can be monolithically fabricated by using standard back-end-of-line (BEOL) techniques [63].

Figure 2.6: An MTJ cell is integrated with an access transistor. Different control signal lines (SL, BL, WL) are shown. Applying suitable biases in these signals, an MTJ cell is written and read [46].

#### 2.4 Spin Valve

A spin valve (SV) (shown in Fig. 2.1(a)) has a structure analogous to an MTJ, but the spacer layer consists of a conductive material. The basic operation of a spin valve is almost similar to an MTJ's except the electron transport mechanism. The electrons are transported through this device by scattering. Electrons with a particular spin get accelerated while passing through a ferromagnetic layer; consequently, they scatter from it. These scattered electrons pass through the conductive spacer layer to the free layer to change their magnetization. Like an MTJ, a spin valve also exhibits two different resistances for parallel and antiparallel configuration. However, resistance difference, in this case, is termed as "Giant Magnetoresistance (GMR)." As the conductive ferromagnetic layers are separated by the conductive spacer layer, the GMR value is expected to be low. Also,

the critical switching current density for a spin valve is relatively high ( $\sim 10^7 - 10^8 A/cm^2$  [64, 65]) which hinders the integration with current CMOS technology.

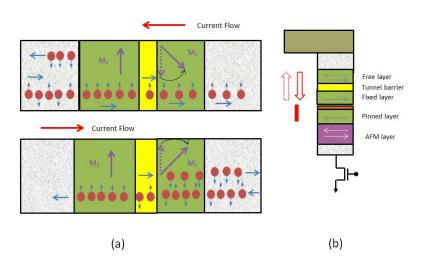

#### 2.5 Domain Wall Memories

Spintronic domain-wall memory (DWM)—also referred to as "Racetrack" memory—recently proposed and demonstrated by IBM [66], is a promising candidate to over- come density limitations while retaining the static energy benefits of STT-MRAM. DWM is constructed from ferromagentic nanowires—also referred to as "tapes" or "racetracks"—separated into domains and connected to a single (or possibly a few) access transistor(s) to create access ports, much like STT-MRAM. DWM conserves the advantages of STT-MRAM while increasing the storage density by up to  $10 \times [67]$  and has a theoretical area per data bit as small as  $2F^2$  [68], where F is the technology feature size. Data access is obtained by shifting the magnetic domains along the nanowire and aligning the target domain to an access device. After alignment, data access is identical to STT-MRAM. DWM demonstrations of memory array structures [69] and content addressable memories (CAMs) [70] show fabrication feasibility with great potential for density, performance, and power consumption.

Unlike the single domain circular nano-magnetic disk, in ferromagnetic nanowires, there exist multiple magnetic domains. The magnetic states of adjacent domains are not parallel to balance the exchange and anisotropic energies [71]. In between two adjacent domains, a mobile non-magnetic barrier, known as domain wall (DW), is present. Mobilization of a domain wall present in a magnetic nanowire, makes them promising as a futuristic device for data storage [72] and logic applications [73]. Under the influence of applied magnetic field, domain walls propagate through the magnetic nanowire. Later, current-driven propagation has been proposed making this system useful for computation. Fig. 2.7 shows a schematic of a magnetic nanowire with domain wall. The micromagnetics of a domain wall propagation can be estimated by the Landau-Lifshitz-Gilbert (LLG) equation [74]:

$$\dot{\vec{m}} = \lambda_0 \vec{H} \times \vec{m} + \alpha \vec{m} \times \dot{\vec{m}} - (\vec{u}.\vec{\Delta})\vec{m}$$

The velocity of propagation of domain walls in a nanowire is an important figure of merit. In the simplest model [75, 76] for a DW motion, the velocity is a function of applied magnetic field

as  $u = \mu H$ , where the mobility,  $\mu = \frac{\gamma \Delta}{\alpha}$ , depends on the gyromagnetic ratio  $(\gamma)$ , Gilbert Damping factor  $(\alpha)$ , and the width of the domain wall  $(\Delta)$ .

Current-driven movement of domain walls is theoretically developed by Kohno et al. [77]. In their research work, they explained the effects of current injection in a magnetic nanowire: spin transfer and momentum transfer. Parkin et al. [78] experimentally demonstrated the current-controlled domain wall motion. The magnetization direction (arrows) of a domain is programmed to store either bit '1' or bit '0'. Several transistors are connected to the stripe to perform read, write, and shift operations, respectively. They are called read access port.

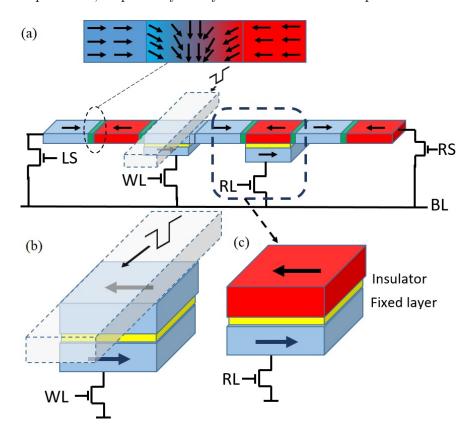

Figure 2.7: (a) Structure of the strip containing 7 bits; (b) write port of DWM nanowire; (c) an MTJ as read-port.

#### 2.6 Application of Spintronic Devices

Different manipulation of that three terms in Eqn. 4.2 has made possible to use MTJs in a wide range of applications, for example, in memory applications as Magnetoresistive Random Access Memory (MRAM) [79], in oscillator domain as Spin Torque Nano-Oscillator (STNO) [80], as

computing elements in memory paradigm [81], and in Non-Boolean Computing domain [82, 83, 84] in many ways.

When the damping in free layer magnetization dynamics is more significant, the magnetization can be in two ground states, parallel, or anti-parallel to the direction of the fixed layer magnetization; this leads to the use of MTJ for memory applications. If a sufficient amount of bias current is passed through an MTJ, the damping will be nullified, and the free layer magnetization will not be settled to any of the ground states. Rather, it exhibits an oscillatory behavior [85]. This phenomenon is exploited while MTJs are being used as nano-oscillator.

#### 2.6.1 Memory Applications

In recent times, spin based memories (MRAM, STT-MRAM) have gained a lot of attention among the researchers and memory industries. The salient features of spin memories such as non-volatility, low switching energy, fast operation, high endurance, and unlimited retention make them promising candidates not only for data storage but also for main memory. Moreover, these memories outperform the other memories while operating in unfavorable conditions. Memory requirement in embedded systems can leverage this quality for operating in an adverse environment. As we are focusing on the non-Boolean computation by spintronic devices in this book, detailed description of the reading and writing operation in memory is beyond our scope. However, interested readers are encouraged to explore these articles [47, 86] for an in-depth insight.

#### 2.6.2 GMR Sensors

In earlier days, GMR based nanosensors were used as the read head of computer hard drives [27, 87]. They can sense the change of local magnetic field by changing their electrical resistances. Later, these nanosensors have been exploited in different areas especially in biosensing. A GMR based biosensor was proposed in [88] for DNA sensing. A biochip based on GMR was proposed for DNA detection and HPV genotyping in [89]. Apart from this, in [90], GMR based biosensors exhibit better performance than the conventional probe in sensing protein for the diagnosis of heart diseases.

#### 2.6.3 Spin Torque Nano-Oscillator

The operation of a Spin Torque Nano-Oscillators (STNO) relies on the current-driven oscillation of magnetization resulting self-sustaining oscillatory changes in the resistance of the device [80]. The oscillation of these devices evolves from the interaction between intensive nonlinear magnetization process and the spin dependent transport through the magnetic heterostructures. The simple configuration of an STNO consists of a relatively thick fixed magnetic layer, which serves as a polarizer, a non-magnetic spacer, and a relatively thin magnetic free layer as shown in Fig. 3.5a.

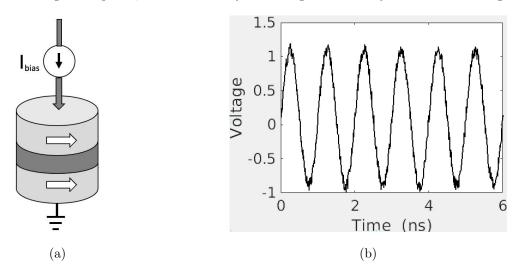

Figure 2.8: (a) Basic configuration of an STNO with a dc bias current. (b) Microwave voltage is generated due to the precessional dynamics in the free layer.

A dc current gets spin-polarized while passing through the polarizer. When this spin polarized current is large enough to transfer sufficient STT to cancel out the intrinsic damping losses of the free layer, a steady-state magnetization precession occurs. The magnetoresistive (MR) effect converts the magnetization oscillation to a microwave voltage (in Fig. 3.5b).

The STNOs have attained a significant attention in recent past for computing and microwave applications [37]. In computing paradigm, the information is coded as the frequency of oscillation of the STNOs. Hence, quantification of the frequency of an STNO is of critical importance. The frequency of oscillation of the free layer of an STNO is approximated by the following equation [91]:

$$f_N(\theta,\zeta) = \frac{|\gamma|}{2\pi} \sqrt{H[H + (\frac{M_0}{\zeta})\cos^2\theta]}$$

(2.8)

where H and  $\theta$  represents internal magnetization field magnitude and direction.  $M_0$  is the free layer magnetization vector magnitude and  $\zeta$ , called supercriticality, can be expressed by

$$\zeta = \frac{I}{I_{th}} \tag{2.9}$$

where I and  $I_{th}$  are the applied and threshold currents respectively.

#### 2.6.4 All-Spin Logic Device (ASLD)

Though the spintronic devices discussed above, considers the neglected electron spin as a state variable besides charge, still these devices require spin-to-charge conversion. Thus they demand extra circuitry, and the performance degrades due to the conversion efficiency. Behtash Behin-Aein et al. proposed a novel device, know as all-spin logic device [92], which claims to be completely spin based. Unlike the domain wall logic and quantum cellular automata (MQCA), this novel scheme promises selectivity during information propagation even though DW and MQCA do not require spin-to-charge conversion.

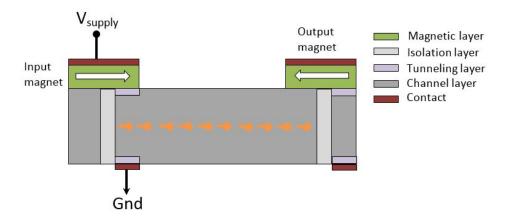

Figure 2.9: Anatomy of a basic all spin logic Device.

The very first schematic of the proposed device is depicted in Fig. 2.9 that shows two single layer nanomagnets (one input magnet and another one is for output) are mounted on a metallic conductor. The magnetization of the output magnet can be switched depending on the polarized current coming from the input magnet through the metallic channel. It is worth mentioning that, the current is polarized according to the information stored while passing through the input magnet.

Sharad *et al.* proposed an almost similar device, termed as Lateral Spin Valve (LSV) [81]. The device operation is almost similar to that of ASLD. Like ASLD, LSV also uses non-local spins and uses Bennett-clocking during operation.

#### 2.6.5 Nanomagnetic Energy Minimizing Co-processor

Recently Bhanja *et al.* proposed a novel nanomagnetic co-processor [82] (Fig. 2.10), to solve the quadratic optimization problems arising in computer vision paradigm. The working principle of this co-processor is based on "let physics do the computation" as it uses the energy minimization framework of a 2-D grid of nanomagnets to solve the optimization problems.

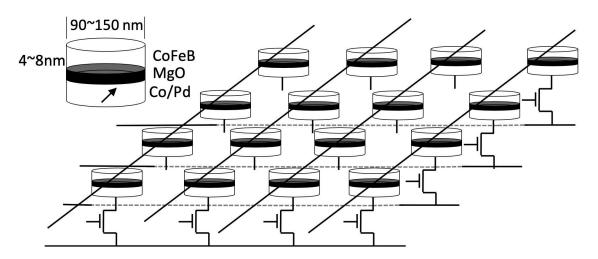

Figure 2.10: A sketch of the nanomagnetic co-processor.

A set of omnipresent and non-parallelizable quadratic optimization problems may benefit from harnessing the energy minimization framework of a 2-D array of nanomagnets, named as "Magnetic Energy Minimization Co-Processor (MEMCoP)" [82, 93]. The original problem is mapped into a 2-D grid of interacting magnets where the optimization is accomplished by the relaxation physics of the magnets themselves. In essence, given a specific instance of the problem, we will arrive at a particular magnetic layout (Fig. 2.10), the relaxed magnetic state of which will be the solution to the original problem. The output magnetization of each cell can be in two states: Single Domain state, in which the remanence is the same as the saturation magnetization and Vortex Domain state, which has no zero in-plane remanence rather shows a curling in-plane magnetic configuration [48].

In computer vision domain, there are three steps regarding the object recognition: 1) feature extraction, 2) perceptual grouping, and 3) object matching. The first step is done by extraction of local features i.e. edges, points and regions using different algorithms for edge detection. Recognizing the salient edge segments of the significant objects is the second phase, perceptual organization. The last one is the object matching between the output of the second step and the database. The quadratic optimization problem in these steps, having a non-convex objective function, is an unconstrained optimization problem. Though feature extraction, in some cases, leverages some hardware platform to be faster, perceptual grouping still relies on the software for computation which is computationally expensive [94].

# 2.7 Conclusion

This chapter discussed the spintronic devices for storage and computation and the key physical properties of them. We reviewed the multi-layer structures, especially MTJs, and the concept of TMR. Later we detailed the generation of STT and STT-based writing. Thereafter we discussed domain wall memories as well its basic operations. We then discussed the use of MTJs as spintorque-nano-oscillator. The all spin logic device is also briefly discussed in this chapter. Finally, we have covered the basic structure and working principle of MEMCoP. In the next chapters, we will focus on the read techniques, and the SOT-mediated reconfiguration of MEMCoP.

### Chapter 3: Reading of Magnetic Energy Minimizing Co-Processor

#### 3.1 Introduction

Alternative computing paradigms targeting heavy data applications is benefited from computing in memory framework [95, 96, 97]. In these applications, the advantage of using spin based memories is twofold: non-volatile storage, and in-memory computation. In this chapter, we discuss a novel computing paradigm that demonstrates computationally complex quadratic optimization problems might have a better solution regarding energy efficiency, and speed through a magnet based hardware [98] than the conventional software based approach. Additionally, the output of that framework is independent of the problem size. The key principle of this hardware is "Let Physics do the computation" as it harnesses the innate energy minimization phenomenon of a grid of nanomagnets to solve quadratic optimization problems, often arose in computer vision domain.

This form of non-Boolean computing impacts a wide range of critical and pervasive application domains based on the Energy Minimization-based optimization framework. Most conventional approaches to solve such problems rely on search-based simulated annealing, neural networks, and genetic algorithms. Apart from a few algorithmic approaches like graph-cuts, these methods are computationally hard. A few example application domains where this work will accelerate computation are: (a) protein-folding problems and drug discovery [99], in social media [100, 101], in error correcting codes [102], in support vector machines [103] and in inferencing Markov Random Fields (graphical Probabilistic Models) [104, 105, 106, 107, 108]. In this chapter<sup>3.1</sup>, we discusses the read mechanisms of a magnetic hardware solving non-Boolean problems.

<sup>&</sup>lt;sup>3.1</sup>This chapter was published in IEEE Transactions on Nanotechnology 17.2 (2018): 368-372, "Reading Nanomagnetic Energy Minimizing Coprocessor.", Roxy, Kawsher A., and Sanjukta Bhanja, and in 2017 IEEE 17th International Conference on Nanotechnology (IEEE-NANO), pp. 1019-1022. IEEE, 2017, "Exploring the readability of nano-magnetic energy minimizing co-processor.", Roxy, Kawsher A., and Sanjukta Bhanja, and in 2017 IEEE 60th International Midwest Symposium on Circuits and Systems (MWSCAS), pp. 413-416. IEEE, 2017, "Variability tolerant reading of nanomagnetic energy minimizing co-processor.", Roxy, Kawsher A., and Sanjukta Bhanja. Permissions attached in Appendix A.

# 3.2 Quadratic Optimization via Energy Minimization of Nanomagnets

Quadratic optimization is a classical combinatorial optimization problem, where we want to minimize a quadratic function over the unknown variables. Let us denote the n unknown variables by a vector  $\mathbf{x}$  of dimension n. The solution is constrained such that the magnitude of the vector is 1, i.e. it lies on a n-dimensional hypersphere. The problem is formally expressed as  $\min \mathbf{x}^T \mathbf{A} \mathbf{x} = \min \sum_i \sum_j a_{ij} x_i x_j$  such that  $\mathbf{x}^T \mathbf{x} = \sum_i x_i^2 = 1$  where  $\mathbf{A}$  is a real symmetric matrix of size n by n. In the discrete version of the problem, the components of the vector  $\mathbf{x}$ ,  $x_i$ 's, are constrained to be  $\pm 1$ . It is well-known that this optimization is NP-hard [109, 110]. Different heuristic or approximation algorithms are usually based on continuous relaxations of the original discrete problems in which vector-valued binary variables are replaced by continuous variables. From the solution of the continuous problem, the discrete solution is derived. We outline one such solution that we can implement using magnets.

# 3.2.1 A Case Study-Perceptual Grouping in Computer Vision

There are many problems in computer vision that require binary quadratic optimization such as motion segmentation [111], correspondences [112], figure/ground segmentation [113], clustering [114], grouping [115], subgraph matching [116], and digital matting [117]. For demonstration purposes, we focus on one such vision problem, namely that of feature grouping for object recognition [115].

Given a set of n features such as straight lines, a type of low-level feature, the task is to find the subject of feature that could possibly come from the same object. Let  $x_i$  denote the importance or saliency of the i-th line; larger values denotes importance. Between every pair of edge line we associate affinity energies,  $A_{ij}$  to capture the perceptual saliency of the relationship between them [115].

$$A_{ij} = \sqrt{l_i l_j} e^{-\frac{o_{ij}}{\max(l_i, l_j)}} e^{-\frac{d_{min}}{\max(l_i, l_j)}} \sin^2(2\theta_{ij})$$

(3.1)

where  $l_i$  and  $l_j$  are the lengths of the *i*-th and *j*-th features,  $o_{ij}$  is the overlap,  $\theta_{ij}$  is the angle, and  $d_{min}$  is the minimum distance between the two straight lines. If two straight lines are parallel to each other then they are likely to belong to one object and hence the affinity should be high. Similarly, lines that are close together are more likely to be associated together. The quantitative

forms of the affinity function vary in different implementation, but qualitatively they capture similar aspects.

$$\sum_{i=1}^{N} \sum_{j=i+1}^{N} a_{ij} x_i x_j + \lambda \sum_{i=1}^{N} x_i + \kappa$$

(3.2)

The goal is to find a group, x, such that total affinity energy in Eq. 3.2 is maximized. N is the total number of edge segments.  $\lambda$  takes the value of -1.  $\kappa$  is the number of edge segments in the salient group. This is a quadratic optimization problem.

### 3.2.2 Total Magnetic Energy in the Magnetic System

The total magnetic energy in the magnetic system, can be calculated from the summation of all the magnetic coupling energies between each other and summation of the internal magnetic energy of all the nanomagnetic disks. The total magnetic energy of the magnetic system with N nanomagnetic disks can be expressed as:

$$E_{total} = \sum_{i=1}^{N} \sum_{j=1+1}^{N} E_{ij} + \sum_{i=1}^{N} E_{i}$$

(3.3)

where  $E_{ij}$  is the magnetic coupling energy between the  $i^{th}$  and  $j^{th}$  nanomagnetic disk and  $E_i$  is the internal magnetic energy of the  $i^{th}$  nanomagnetic disk.

$$E_{ij} = \gamma e^{-\sigma r_{ij}} \vec{S}_i \cdot \vec{S}_j \tag{3.4}$$

$$E_i = \beta |\vec{S}_i| + \omega \tag{3.5}$$

$$E_{total} = \gamma \sum_{i=1}^{N} \sum_{j=i+1}^{N} e^{-\sigma r_{ij}} \vec{S}_i \cdot \vec{S}_j + \beta \sum_{i=1}^{N} |\vec{S}_i| + N\omega$$

(3.6)

# 3.2.3 Mapping the Optimization Problem to the Magnetic System

The similarity between Eq. 3.2 and Eq. 3.6, which is exploited to map quadratic optimization problems into magnetic layouts using 2-D visualization techniques e.g. multi-dimensional scaling (MDS). The affinity between two line segments is inversely proportional to the distance between

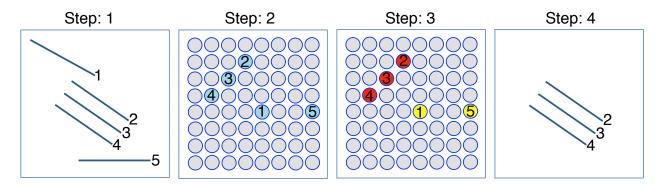

the nanomagnets representing them. Hence, mapping put magnetic dots representing line segments from same objects close to each other, and different object far away. Fig.3.1 depicts the steps involved in determining the salient edges using the nanomagnetic co-processor. The compiler maps each edge segment to a single nanomagnet in the nanomagnetic co-processor grid. The steps of mapping are:

- 1. Step 1: Edge detection, affinity matrix calculation, multidimensional scaling and mapping of features (edge segments) to nanomagnets).

- 2. Step 2: Activating computing nanomagnets and deactivating non-computing nanomagnets. Each computing nanomagnet represent a feature (edge segment).

- 3. Step 3: Magnetic computing and relaxation. Identification of computing magnet's magnetization state. Red represents single-domain state. Yellow represent vortex states.

- 4. Step 4: Determine the salient features (edge segments) by back tracing the mapping of the single-domain computing nanomagnets with features (edge segments) [82].

After computation, the final magnetization states of all the computing nanomagnets are identified. As each computing nanomagnet represent an edge, the single domain nanomagnets are back traced to corresponding edges and are identified as salient edge segments.

Figure 3.1: Steps involved in problem mapping into nanomagnetic co-processor.

# 3.2.4 Translating Output of the Problem from Magnetic States

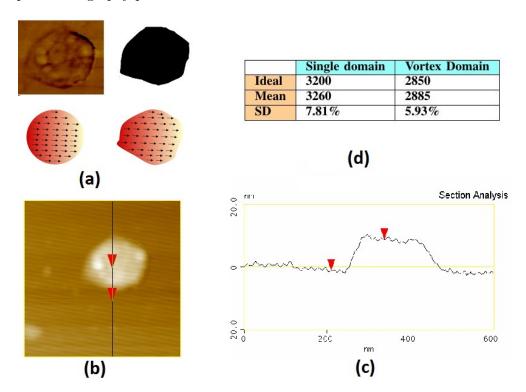

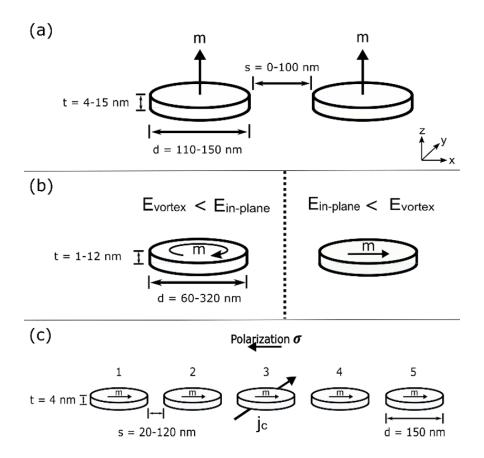

In case of a circular magnetic nanodisk, the diameter and thickness are the key factors that determine the magnetic state. Literature [48] has established the dependency of magnetization on these parameters. One can understand this relation by considering D as the diameter, and t as the thickness of a circular nanomagnet. Formation of a single domain or multidomain can be explicitly interpreted by the aspect ratio, m = D/t. m < 1 ensures that the magnetic disk only has two (single domain or vortex) states. A phase boundary between the single domain and vortex domain was outlined in [118] for a 2D grid of closely spaced nanomagnets as shown in Fig. 6.2a. It is evident experimentally from Fig. 6.2c that, one nanomagnetic disk can exhibit in-plane single domain behavior when interacting with neighboring magnetic cells, and vortex domain behavior when isolated [119].

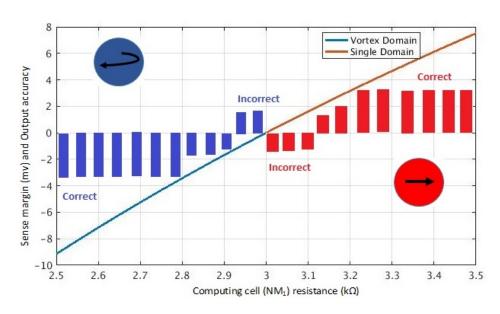

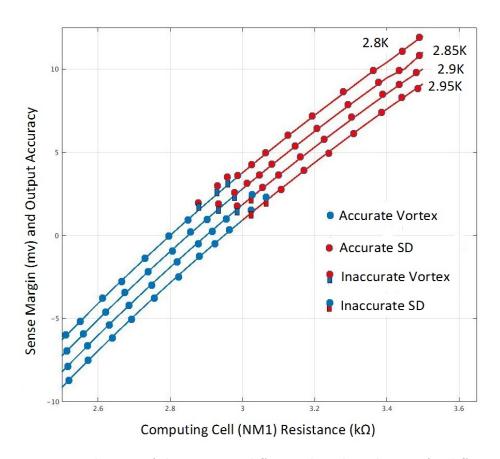

Figure 3.2: (a) Phase plot; (b) Cell dimension and distance between them; (c) Closely placed nanomagnets behave as single domain, otherwise vortex domain.

### 3.3 Electrical Reading of the Output

The resistance differential between these states aids in detecting the magnetization of the cells, in other words, the output of the problem. However, absence of shape anisotropy in the circular nanomagnetic cells substantially lowers the resistance values, thus making the read process more challenging. We investigated three different methods for finding an efficient mechanism to read the magnetic cells, and studied the variation of resistances of the cells due to the fabrication imperfection. Since the resistance difference between the magnetic states, and consequently the sense margin is low, maintaining a higher accuracy is challenging. Moreover, non-destructive reading,

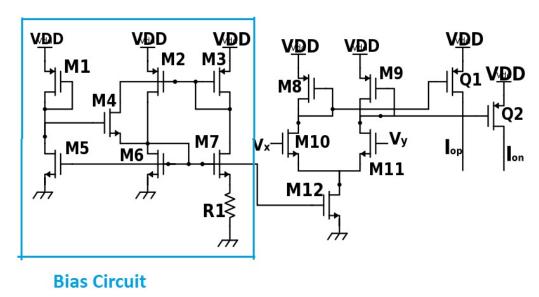

and the smaller resistances potentially lower the sense margin making the reading mechanisms vulnerable to the process variations. To make the process more resilient, we proposed an additional pre-amplifier, and with this we demonstrated that the sense margin can be improved by at least 73%.

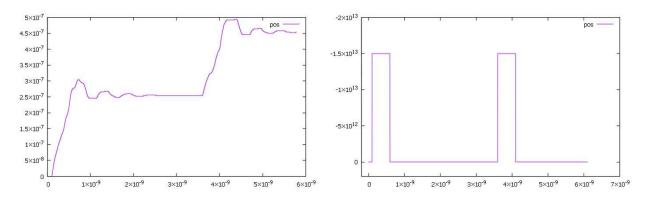

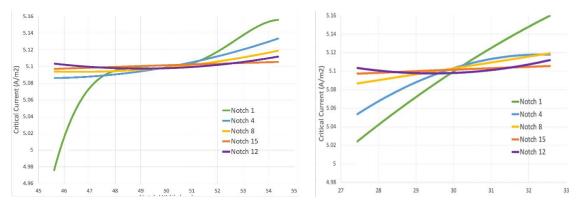

# 3.3.1 Structure and Resistance Modelling of a Cell